- ��IC�ؼ���

�����������ŵ��ӿƼ�����˾

- ���һ��֣�

Ӫҵִ�գ��������Ӫģʽ��ó��/����/�������ڵ������㶫 ������ҵ��վ��

Ӫҵִ�գ��������Ӫģʽ��ó��/����/�������ڵ������㶫 ������ҵ��վ��

http://www.zlxele.com

�ղر���˾ ������716682

��ҵ����

- ���֤����

- ��Ա���ͣ�

- ��Ա���ޣ�16��

- ����IM��

- ��ַ�������и���������·�ʺ��¶����ò�����7A��

- ���棺0755-23956688

- E-mail��Lee@zlxele.com

��Ʒ����

- ����������(1)

- ��ѹ������(6)

- ���ض�����(4)

- ˲̬(��)���ƶ�����(101)

- ���ʶ�����(2)

- ESD���������(1)

- ����������(9)

- Ф�ػ�������(19)

- TVP��(1)

- ����������(1)

- ����Ƶ/��Ƶ������(18)

- ����(���ֶ�)������(2)

- ����������(55)

- MOSFET(57)

- IGBTģ��(2)

- GTR���ֶ�ģ��(5)

- ������ЧӦ��ģ��(2)

- ����ɿع�(��բ��)(2)

- ˫��ɿع�(��բ��)(16)

- �ɿع�(��բ��)ģ��(10)

- ��Ƭ��MCU(291)

- ��Ƭ�������(1)

- ��Ƭ/Ƭʽ����(5)

- �۶�/����˿����(1)

- ����Ƶ����(1)

- ��Ĥ����(2)

- ��������(6)

- ѹ������(5)

- ��������(6)

- �������(9)

- ģ���Դ/��Դģ��(1)

- ��Ƭ����(1)

- ����������(78)

- ����������(1)

- ��Ƭ/Ƭʽ����(1)

- DIP/���뿪��(1)

- ˫Ͷ����(1)

- ���������豸���(2)

- ��ѧ������(2)

- ��(ʪ)�ȴ�����(10)

- ����/����������(1)

- ѹ��������(6)

- ���ٶȴ�����(4)

- ����/����/������(2)

- ����������(1)

- ��Ƭ����˿(26)

- �����ܱ���˿(10)

- �մɹܱ���˿(23)

- �Իָ�����˿(8)

- ����/��Ƭ����˿(2)

- �۶ϱ���˿(1)

- ����˿��/����˿��(4)

- ��������˿(11)

- ����ŵ��(1)

- ͨѶ��ѹ��(1)

- ������ѹ�����(1)

- �����̵���(1)

- �����߷����(1)

- ���������(����)(11)

- LED����(54)

- ����LED��ز�Ʒ������(1)

- ����ʽPLC(1)

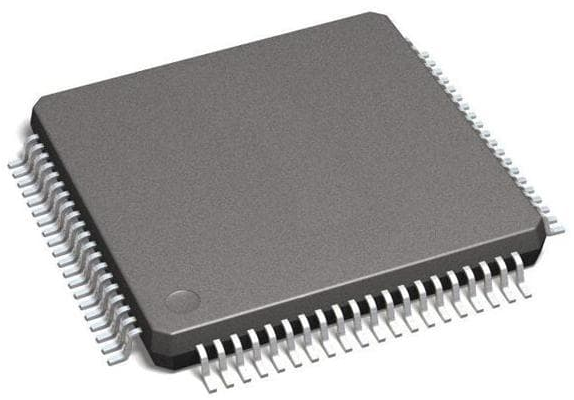

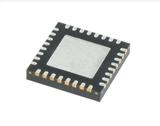

SPC5606SF2VLQ6 ������ NXP

SPC5606SF2VLQ6

NXP

32λ

64 MHz

48 kB

105 I/O

3.3 V, 5 V

��ز�Ʒ

��Ʒ��Ϣ

SPC5606SF2VLQ6

32����� - MCU 32BIT 1M FL 48K RAM

Document overview

This document describes the device features and highlights important electrical and physical characteristics. For functional characteristics, see the MPC5606S Microcontroller Reference Manual.

Description

The SPC5606SF2VLQ6 family of chips is designed to enable the development of automotive instrument cluster applications by providing a single-chip solution capable of hosting real-time applications and driving a TFT display directly using an on-chip color TFT display controller.

Flash memory

The SPC5606SF2VLQ6 microcontroller has the following flash memory features:

• As nuch as 1 MB of burst flash memory

�� Typical flash memory access time: 0 wait state for buffer hits, 2 wait states for page buffer miss at 64 MHz

�� Two 4128-bit page buffers with programmable prefetch control

�C One set of page buffers can be allocated for code-only, fixed partitions of code and data, all available for any access

�C One set of page buffers allocated to Display Controller Unit and the eDMA

�� 64-bit ECC with single-bit correction, double-bit detection for data integrity

�� 64 KB data flash memory �� separate 416 KB flash block for EEPROM emulation with prefetch buffer and 128-bit data access port

Memory Protection Unit (MPU) SPC5606SF2VLQ6

The MPU features the following:

• 12 region descriptors for per-master protection

• Start and end address defined with 32-byte granularity

• Overlapping regions supported

• Protection attributes can optionally include process ID

• Protection offered for three concurrent read ports

• Read and write attributes for all masters

• Execute and supervisor/user mode attributes for processor masters