- ��IC�ؼ���

�����������ŵ��ӿƼ�����˾

- ���һ��֣�

Ӫҵִ�գ��������Ӫģʽ��ó��/����/�������ڵ������㶫 ������ҵ��վ��

Ӫҵִ�գ��������Ӫģʽ��ó��/����/�������ڵ������㶫 ������ҵ��վ��

http://www.zlxele.com

�ղر���˾ ������717341

��ҵ����

- ���֤����

- ��Ա���ͣ�

- ��Ա���ޣ�16��

- ����IM��

- ��ַ�������и���������·�ʺ��¶����ò�����7A��

- ���棺0755-23956688

- E-mail��Lee@zlxele.com

��Ʒ����

- ����������(1)

- ��ѹ������(6)

- ���ض�����(4)

- ˲̬(��)���ƶ�����(101)

- ���ʶ�����(2)

- ESD���������(1)

- ����������(9)

- Ф�ػ�������(19)

- TVP��(1)

- ����������(1)

- ����Ƶ/��Ƶ������(18)

- ����(���ֶ�)������(2)

- ����������(55)

- MOSFET(57)

- IGBTģ��(2)

- GTR���ֶ�ģ��(5)

- ������ЧӦ��ģ��(2)

- ����ɿع�(��բ��)(2)

- ˫��ɿع�(��բ��)(16)

- �ɿع�(��բ��)ģ��(10)

- ��Ƭ��MCU(291)

- ��Ƭ�������(1)

- ��Ƭ/Ƭʽ����(5)

- �۶�/����˿����(1)

- ����Ƶ����(1)

- ��Ĥ����(2)

- ��������(6)

- ѹ������(5)

- ��������(6)

- �������(9)

- ģ���Դ/��Դģ��(1)

- ��Ƭ����(1)

- ����������(78)

- ����������(1)

- ��Ƭ/Ƭʽ����(1)

- DIP/���뿪��(1)

- ˫Ͷ����(1)

- ���������豸���(2)

- ��ѧ������(2)

- ��(ʪ)�ȴ�����(10)

- ����/����������(1)

- ѹ��������(6)

- ���ٶȴ�����(4)

- ����/����/������(2)

- ����������(1)

- ��Ƭ����˿(26)

- �����ܱ���˿(10)

- �մɹܱ���˿(23)

- �Իָ�����˿(8)

- ����/��Ƭ����˿(2)

- �۶ϱ���˿(1)

- ����˿��/����˿��(4)

- ��������˿(11)

- ����ŵ��(1)

- ͨѶ��ѹ��(1)

- ������ѹ�����(1)

- �����̵���(1)

- �����߷����(1)

- ���������(����)(11)

- LED����(54)

- ����LED��ز�Ʒ������(1)

- ����ʽPLC(1)

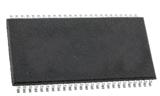

IS42S16160G-7TLI ��̬�����ȡ�洢��

256 Mbit

143 MHz

7 ns

16 bit

- 40 ��

85 ��

��ز�Ʒ

��Ʒ��Ϣ

IS42S16160G-7TLI

��̬�����ȡ�洢�� 256M 16Mx16 143MHz SDR S��̬�����ȡ�洢��, 3.3V

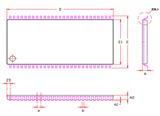

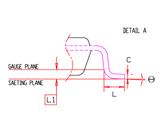

32Meg x 8, 16Meg x16 256Mb SYNCHRONOUS DRAM

OVERVIEW IS42S16160G-7TLI

ISSI's 256Mb Synchronous DRAM achieves high-speed

data transfer using pipeline architecture. All inputs and

outputs signals refer to the rising edge of the clock input.

The 256Mb SDRAM is organized as follows.

The IS42S16160G-7TLI 256Mb SDRAM is a high speed CMOS, dynamic

random-access memory designed to operate in 3.3V Vdd

and 3.3V Vddq memory systems containing 268,435,456

bits. Internally configured as a quad-bank DRAM with a

synchronous interface. Each 67,108,864-bit bank is organized

as 8,192 rows by 512 columns by 16 bits or 8,192

rows by 1,024 columns by 8 bits.

FEATURES IS42S16160G-7TLI

• Clock frequency: 200,166, 143 MHz

• Fully synchronous; all signals referenced to a

positive clock edge

• Internal bank for hiding row access/precharge

• Single Power supply: 3.3V + 0.3V

• LVTTL interface

• Programmable burst length

�C (1, 2, 4, 8, full page)

• Programmable burst sequence:

Sequential/Interleave

• Auto Refresh (CBR)

• Self Refresh

• 8K refresh cycles every 32 ms (A2 grade) or

64 ms (commercial, industrial, A1 grade)

• Random column address every clock cycle

• Programmable CAS latency (2, 3 clocks)

• Burst read/write and burst read/single write

operations capability

• Burst termination by burst stop and precharge

command