- 非IC关键词

深圳市中立信电子科技有限公司

- 卖家积分:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

http://www.zlxele.com

收藏本公司 人气:986455

企业档案

- 相关证件:

- 会员类型:

- 会员年限:17年

- 阿库IM:

- 地址:深圳市福田区彩田路彩虹新都大厦彩荟阁7A室

- 传真:0755-23956688

- E-mail:Lee@zlxele.com

SPC5775KK2MMY3A 微控制器MCU NXP

SPC5775KK2MMY3A

NXP

32位

32位微控制器 - MCU

32-bit Microcontrollers - MCU

Microcontrollers - MCU

1.386 g

相关产品

产品信息

SPC5775KK2MMY3A

32位微控制器 - MCU 4M FLASH, 1.5M RAM, Automotive Qualified

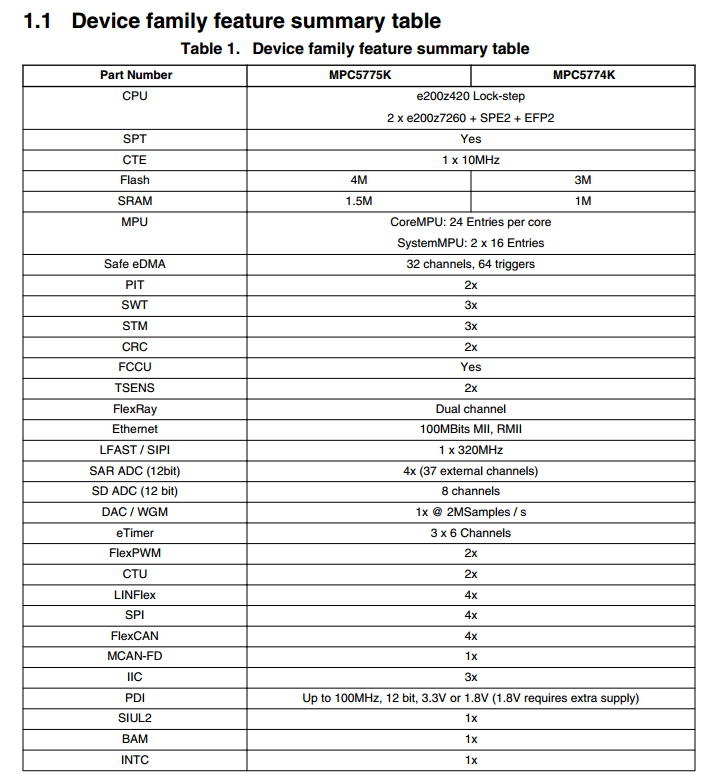

Feature summary SPC5775KK2MMY3A

The on-chip modules within the MPC5775K include the following features:

• 32-bit CPU (e200z420) based on Power Architecture technology with delayed lock step checker core, dual issue and Harvard bus architecture

• 8 KB code cache

• 4 KB data cache

• 64 KB data local memory (0-wait state for all read and 32-/64-bit write accesses)

• Wait states possible for backdoor accesses via the crossbar

• Scalar single-precision Floating Point Unit SPC5775KK2MMY3A

• Two 32-bit CPUs (e200z7260) based on Power Architecture technology with dual issue and Harvard bus architecture

• 16 KB code cache with EDC and parity

• 16 KB data cache with EDC and parity

• 64 KB data local memory with ECC (0-wait state for all read and 32/64-bit write accesses)

• Wait states possible for backdoor accesses via the crossbar

Core features SPC5775KK2MMY3A

MPC5775K is a multicore microcontroller unit that:

• Contains one safety core consisting of an e200z420 with an e200z419 checker core running in delayed Lockstep mode

• Contains two cores running independent of each other implemented as z7260 and adding:

• SPE2 4-way integer SIMD engine

• EFP2 2-way single precision floating point engine freedom of interference by placing cores in separate design lakes

• Supports Harvard bus architecture with 64-bit data/instructions and 32-bit addresses

• Provides Nexus 3+ support