- 非IC关键词

深圳市中立信电子科技有限公司

- 卖家积分:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

http://www.zlxele.com

收藏本公司 人气:978983

企业档案

- 相关证件:

- 会员类型:

- 会员年限:17年

- 阿库IM:

- 地址:深圳市福田区彩田路彩虹新都大厦彩荟阁7A室

- 传真:0755-23956688

- E-mail:Lee@zlxele.com

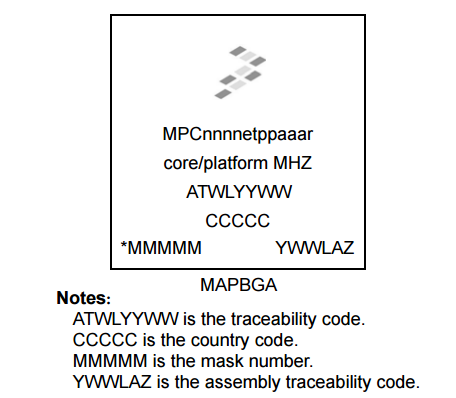

MPC8309CVMAGDCA 微处理器 NXP

MPC8309CVMAGDCA

NXP

32位

32 bit

1 Core

1 V

16 kB

相关产品

产品信息

MPC8309CVMAGDCA

微处理器 - MPU E300 MP EXT TMP

Overview

The MPC8309CVMAGDCA incorporates the e300c3 (MPC603e-based) core built on Power Architecture® technology, which includes 16 Kbytes of each L1 instruction and data caches, dual integer units, and on-chip memory management units (MMUs). The MPC8309 also includes a 32-bit PCI controller, two DMA engines and a 16/32-bit DDR2 memory controller with 8-bit ECC.

Features MPC8309CVMAGDCA

The major features of the device are as follows:

• e300c3 Power Architecture processor core

— Enhanced version of the MPC603e core

— High-performance, superscalar processor core with a four-stage pipeline and low interrupt latency times

— Floating-point, dual integer units, load/store, system register, and branch processing units

— 16-Kbyte instruction cache and 16-Kbyte data cache with lockable capabilities

— Dynamic power management

— Enhanced hardware program debug features

— Software-compatible with Freescale processor families implementing Power Architecture technology

— Separate PLL that is clocked by the system bus clock

— Performance monitor

• QUICC Engine block MPC8309CVMAGDCA

— 32-bit RISC controller for flexible support of the communications peripherals with the following features:

– One clock per instruction

– Separate PLL for operating frequency that is independent of system’s bus and e300 core frequency for power and performance optimization

– 32-bit instruction object code

– Executes code from internal IRAM

– 32-bit arithmetic logic unit (ALU) data path