- 非IC关键词

深圳市中立信电子科技有限公司

- 卖家积分:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

http://www.zlxele.com

收藏本公司 人气:983683

企业档案

- 相关证件:

- 会员类型:

- 会员年限:17年

- 阿库IM:

- 地址:深圳市福田区彩田路彩虹新都大厦彩荟阁7A室

- 传真:0755-23956688

- E-mail:Lee@zlxele.com

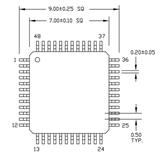

CY8C4245AXI-483 ARM微控制器

CY8C4245AXI-483

Cypress

32位

: 48 MHz

: 12 bit

: 1.8 V

: 4 kB

相关产品

产品信息

CY8C4245AXI-483

ARM微控制器 - MCU 32KB Flash 4KB SRAM PSoC 4

General Description CY8C4245AXI-483

CY8C4245AXI-483 PSoC® 4 is a scalable and reconfigurable platform architecture for a family of programmable embedded system controllers with an ARM® Cortex®-M0 CPU. It combines programmable and reconfigurable analog and digital blocks with flexible automatic routing. The PSoC 4200L product family, based on this platform, is a combination of a microcontroller with digital programmable logic, programmable analog, programmable interconnect, secure expansion of memory off-chip, high-performance analog-to-digital conversion, opamps with Comparator mode, and standard communication and timing peripherals. The PSoC 4200L products will be fully compatible with members of the PSoC 4 platform for new applications and design needs. The programmable analog and digital subsystems allow flexibility and in-field tuning of the design.

Features CY8C4245AXI-483

32-bit MCU Subsystem

■ 48 MHz ARM Cortex-M0 CPU with single-cycle multiply

■ Up to 256 kB of flash with Read Accelerator

■ Up to 32 kB of SRAM

■ DMA engine with 32 channels

Programmable Analog

■ Four opamps that operate in Deep Sleep mode at very low

current levels

■ All opamps have reconfigurable high current pin-drive,

high-bandwidth internal drive, ADC input buffering, and

Comparator modes with flexible connectivity allowing input

connections to any pin

■ Four current DACs (IDACs) for general-purpose or capacitive

sensing applications on any pin

■ Two low-power comparators that operate in Deep Sleep mode

Programmable Digital

■ Eight programmable logic blocks, each with 8 Macrocells and

an 8-bit data path (called universal digital blocks or UDBs)

■ Cypress-provided peripheral component library, user-defined

state machines, and Verilog input