- 非IC关键词

深圳市中立信电子科技有限公司

- 卖家积分:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

营业执照:已审核经营模式:贸易/代理/分销所在地区:广东 深圳企业网站:

http://www.zlxele.com

收藏本公司 人气:985377

企业档案

- 相关证件:

- 会员类型:

- 会员年限:17年

- 阿库IM:

- 地址:深圳市福田区彩田路彩虹新都大厦彩荟阁7A室

- 传真:0755-23956688

- E-mail:Lee@zlxele.com

相关产品

产品信息

IS42S16160G-7TLI

动态随机存取存储器 256M 16Mx16 143MHz SDR S动态随机存取存储器, 3.3V

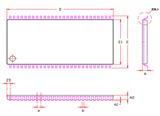

32Meg x 8, 16Meg x16 256Mb SYNCHRONOUS DRAM

OVERVIEW IS42S16160G-7TLI

ISSI's 256Mb Synchronous DRAM achieves high-speed

data transfer using pipeline architecture. All inputs and

outputs signals refer to the rising edge of the clock input.

The 256Mb SDRAM is organized as follows.

The IS42S16160G-7TLI 256Mb SDRAM is a high speed CMOS, dynamic

random-access memory designed to operate in 3.3V Vdd

and 3.3V Vddq memory systems containing 268,435,456

bits. Internally configured as a quad-bank DRAM with a

synchronous interface. Each 67,108,864-bit bank is organized

as 8,192 rows by 512 columns by 16 bits or 8,192

rows by 1,024 columns by 8 bits.

FEATURES IS42S16160G-7TLI

• Clock frequency: 200,166, 143 MHz

• Fully synchronous; all signals referenced to a

positive clock edge

• Internal bank for hiding row access/precharge

• Single Power supply: 3.3V + 0.3V

• LVTTL interface

• Programmable burst length

– (1, 2, 4, 8, full page)

• Programmable burst sequence:

Sequential/Interleave

• Auto Refresh (CBR)

• Self Refresh

• 8K refresh cycles every 32 ms (A2 grade) or

64 ms (commercial, industrial, A1 grade)

• Random column address every clock cycle

• Programmable CAS latency (2, 3 clocks)

• Burst read/write and burst read/single write

operations capability

• Burst termination by burst stop and precharge

command